# **EMSim**: A Fast Layout Level Electromagnetic Emanation Simulation Framework for High Accuracy Pre-Silicon Verifications

Haocheng Ma<sup>1</sup>, Max Panoff<sup>2</sup>, Jiaji He<sup>3</sup>, Yiqiang Zhao<sup>1</sup> and **Yier Jin**<sup>2</sup> <sup>1</sup>Tianjin University, <sup>2</sup>University of Florida, <sup>3</sup>Tsinghua University

#### Outline

- Motivation

- Modeling Framework

- Model Analysis

- Simulation Framework

- Case Studies

- EMSim vs ConvEM

- EMSim vs Silicon Measurements

- Conclusions

#### Outline

- Motivation

- Modeling Framework

- Model Analysis

- Simulation Framework

- Case Studies

- EMSim vs ConvEM

- EMSim vs Silicon Measurements

- Conclusions

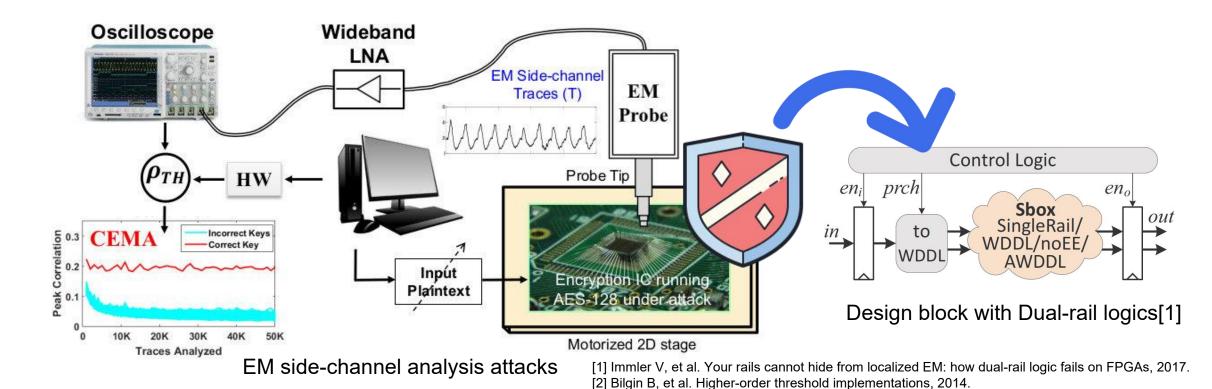

- Increasingly EM side-channel threats targeting ICs

- Rich spatial information, contactless collection

- Break dual-rail logics[1], threshold implementations[2], etc.

- EM side-channel leakage assessment is of importance

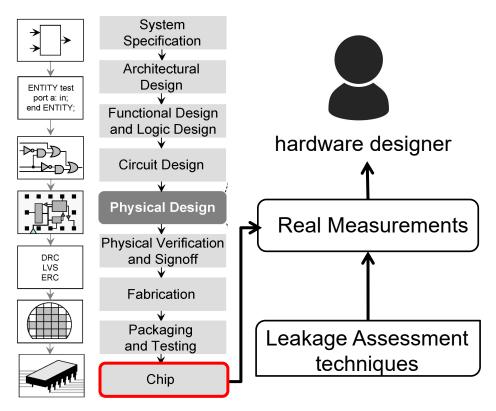

- Post-silicon assesment with real measurements

- Only quantify the security level

- High cost in making design changes

Post-silicon leakage assessment

- EM side-channel leakage assessment is of importance

- Post-silicon assesment with real measurements

- Only quantify the security level

- High cost in making design changes

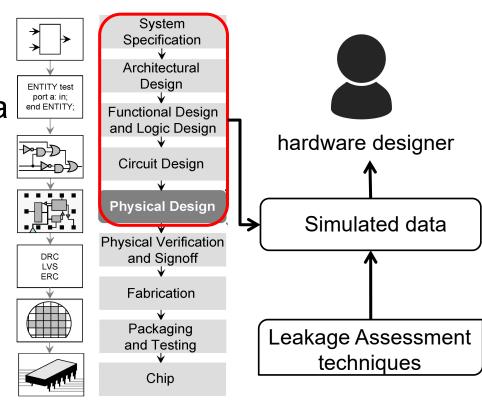

- Pre-silicon assesment with simulated data

- Quantify the security level

- Diagnose vulnerabilities location

- Flexibility in making design changes

- EM simulation with layout data can fully indicate the spatial, temporal and amplitude characteristics of EM emanations

Pre-silicon leakage assessment

- the procedure of the layout-level EM simulation

- Multi-level circuit analysis to obtain the current profiles

- Calculate the probed EM emanations

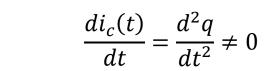

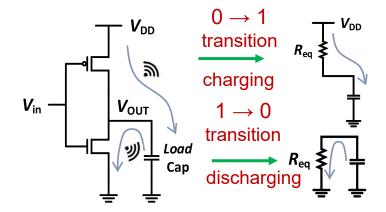

state transitions  $\rightarrow$  changing current

logic cells create varying currents

metal wires emit EM fields

Principle of EM simulation

- the procedure of the layout-level EM simulation

- Multi-level circuit analysis to obtain the current profiles

- Calculate the probed EM emanations

- Existing methods suffer from scalability issues

- Growing circuit sizes, lead to large extracted parasitic networks and complex simulated device models

- Lack of theoretical guidance to simplify the EM simulation

**EMSim**: A Fast Layout Level Electromagnetic Emanation Simulation Framework for High Accuracy Pre-Silicon Verifications

#### Outline

- Motivation

- Modeling Framework

- Model Analysis

- Simulation Framework

- Case Studies

- EMSim vs ConvEM

- EMSim vs Silicon Measurements

- Conclusions

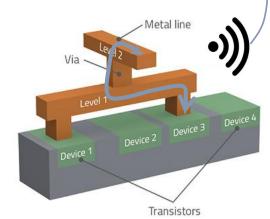

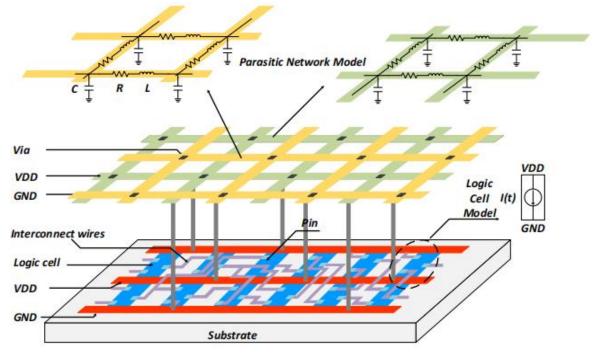

- Physical model of CMOS based ICs

- Logic cell network is formed by groups of transistors on silicon substrate

The power grid combined with interconnect wires, forms the parasitic

network

Physical model of CMOS based ICs

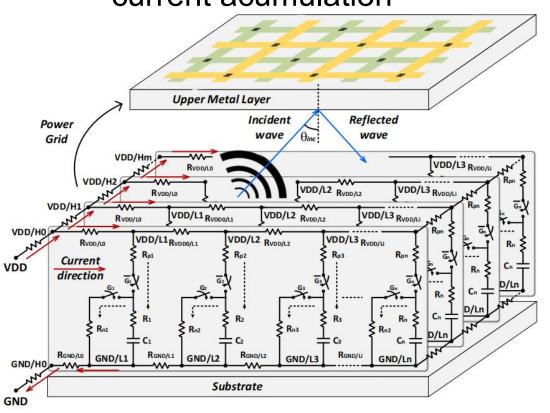

- The genesis of ICs' EM emanations

- Larger currents flows within the power grids in the upper metal layers as current acumulation

VDD: the power pins around the chip die VDD/Hj: power nodes distributed in the top metal layers of the power grid

VDD/Li: Power nodes in the lower metal layers of the power grid

R<sub>i</sub> and C<sub>i</sub>: equivalent resistance and capacitance of load (interconnect wires and cells)

$$\begin{split} I_{VDD} &= \sum_{j=1}^{m} I_{VDD/Hj} = \sum_{j=1}^{m} \sum_{i=1}^{n} I_{VDD/Li} \\ &= \sum_{j=1}^{m} \sum_{i=1}^{n} \left[ \frac{V_{VDD/Li} - V_{GND/Li}}{R_{pi} + R_{si} - 1/jwC_{i}} + I_{short} + I_{leak} \right] \end{split}$$

- The genesis of ICs' EM emanations

- Larger currents flows within the power grids in the upper metal layers as current acumulation

- Due to existence of the metal shielding, EM emanations from lower metal layers hardly propagate to the external environment.

$$R = \frac{(1 - \sqrt{2\varepsilon_0 \omega/\sigma})^2 + 1}{(1 + \sqrt{2\varepsilon_0 \omega/\sigma})^2 + 1} \approx 1 - \sqrt{2\varepsilon_0 \omega/\sigma}$$

electrical conductivity of Cu:  $\sigma = 5.7e7$  S/m vacuum permittivity  $\varepsilon_0 = 8.85e - 12$  F/m  $\omega$  is circular frequency.

Wave reflection when propagating on the metal surface

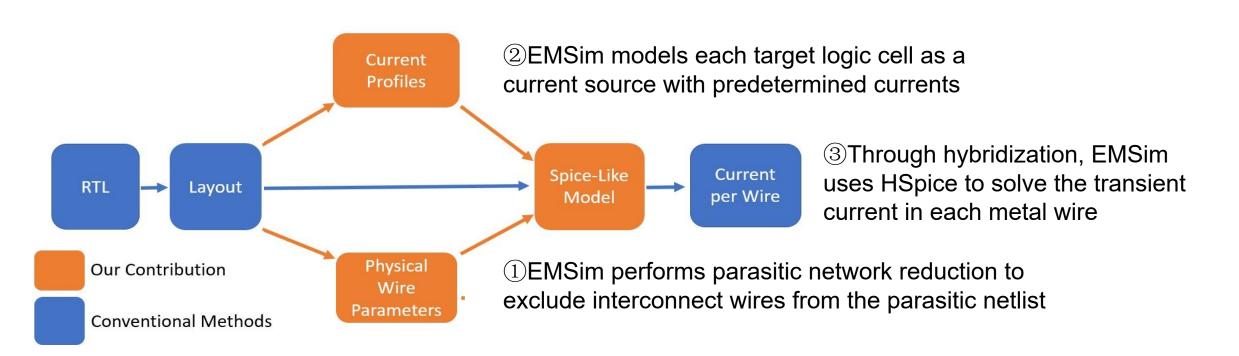

- EMSim Framework

- Data Preparation: RTL-to-GDS flow to create a layout database

- EMSim Framework

- Data Preparation: RTL-to-GDS flow to create a layout database

- Current Analysis: parasitic network reduction, device model approximation

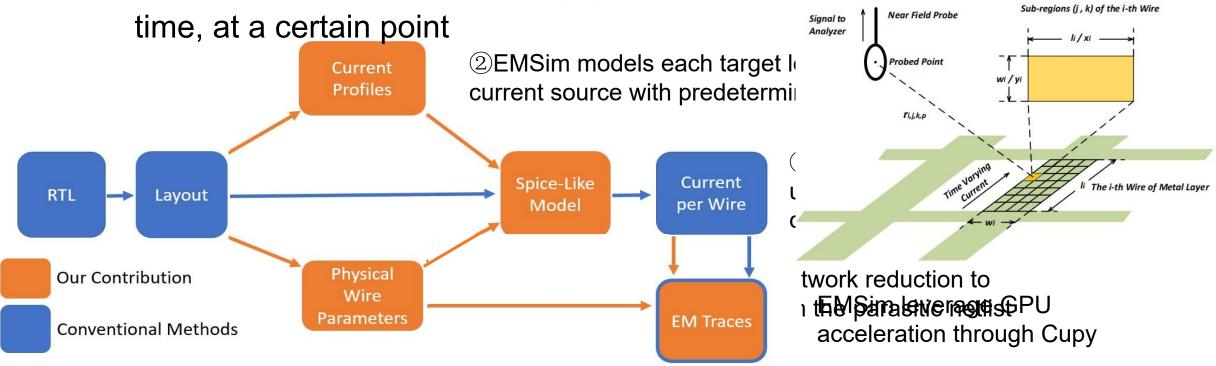

- EMSim Framework

- Data Preparation: RTL-to-GDS flow to create a layout database

- Current Analysis: parasitic network reduction, device model approximation

- Electromagnetic Computation: approximate the magnetic field at a certain

#### Outline

- Motivation

- Modeling Framework

- Model Analysis

- Simulation Framework

- Case Studies

- EMSim vs ConvEM

- EMSim vs Silicon Measurements

- Conclusions

parasitic network reduction

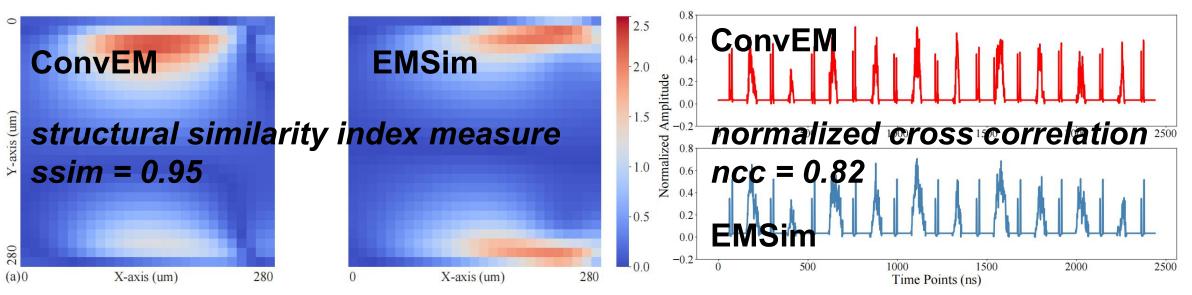

- EMSim vs ConvEM

- Benchmark: 32-bit S-Box design

- Simulation Accuracy

- 1180 nm CMOS technology

- 2900 cells and 31546 wires  $\rightarrow$  754 wires

- ③280.36 um x 280.24 um of die size

- 4 supply voltage 1.8 V

- **5** clock frequency 20 MHz

Comparisons between ConvEM (left) and EMSim (right): (a) magnetic map and (b) correnponding traces.

parasitic network reduction

- EMSim vs ConvEM

- Benchmark: 32-bit S-Box design

- Simulation Accuracy

- Security Evaluation

- ①180 nm CMOS technology

- (2)900 cells and 31546 wires  $\rightarrow$  754 wires

- ③280.36 um x 280.24 um of die size

- 4 supply voltage 1.8 V

- **5**clock frequency 20 MHz

CEMA attacks on the S-Box: (a) correlation map and (b) correlation traces as a function of time points obtained from ConvEM and EMSim.

#### parasitic network reduction

- EMSim vs ConvEM

- Benchmark: 32-bit S-Box design

- Simulation Accuracy

- Security Evaluation

- Computation Cost

- ①180 nm CMOS technology

- (2)900 cells and 31546 wires  $\rightarrow$  754 wires

- ③280.36 um x 280.24 um of die size

- 4 supply voltage 1.8 V

- **5** clock frequency 20 MHz

| Method | Current Simulation   | EM Computation        |

|--------|----------------------|-----------------------|

| ConvEM | 2.017  s             | $0.233 \; s$          |

| EMSIM  | $0.065 \mathrm{\ s}$ | $0.003 \; \mathrm{s}$ |

TABLE II: Real time spent on each simulation time point for a simple 32-bit AES S-Box.

Nelms Institute for the Connected World UNIVERSITY of FLORIDA

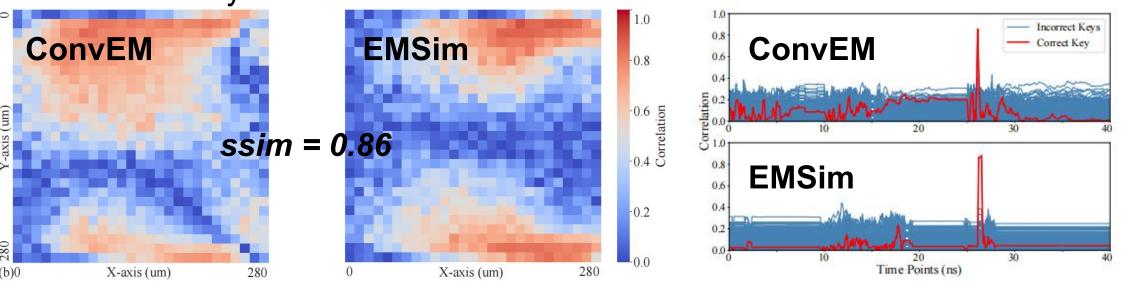

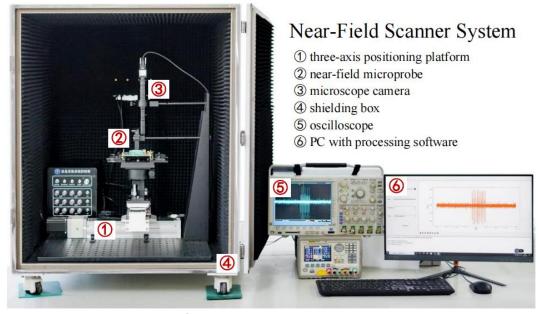

- EMSim vs Silicon Measurements

- Benchmark: 128-bit AES design

The die image of the fabricated AES design.

1)180 nm CMOS technology

2)14559 cells and 733662 wires

3)1.6 mm x 1.3 mm of die size

4)supply voltage 1.8 V

5)clock frequency 25 MHz

365529 for current analysis

1424 for electromagnetic computation

The overview of the experimental setup.

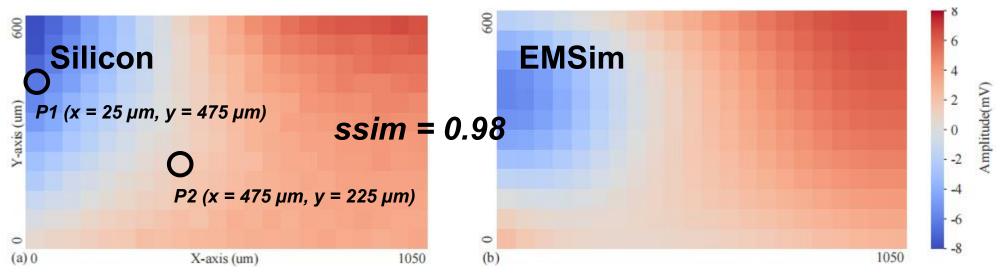

- EMSim vs Silicon Measurements

- Benchmark: 128-bit AES design

- Simulation Accuracy

1)180 nm CMOS technology

2)14559 cells and 733662 wires

3)1.6 mm x 1.3 mm of die size

4)supply voltage 1.8 V

5)clock frequency 25 MHz

365529 for current analysis

1424 for electromagnetic computation

The map of EM signals obtained by (a) silicon measurements, (b) EMSim results

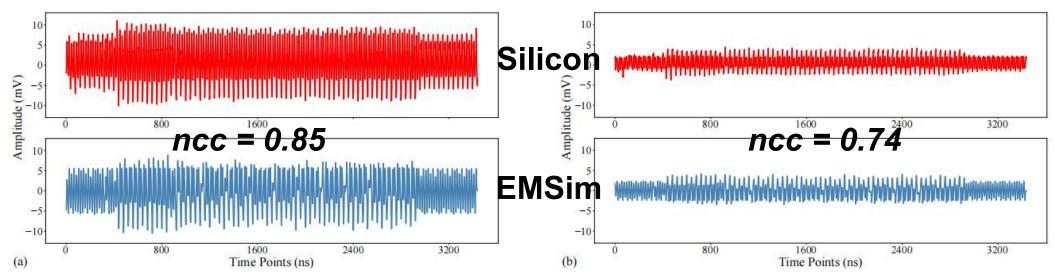

- EMSim vs Silicon Measurements

- Benchmark: 128-bit AES design

- Simulation Accuracy

- 1)180 nm CMOS technology

2)14559 cells and 733662 wires

3)1.6 mm x 1.3 mm of die size

4)supply voltage 1.8 V

- 5 clock frequency 25 MHz

365529 for current analysis

1424 for electromagnetic computation

The comparisons of EM signals obtained by silicon measurements (top) and EMSIM results (bottom), at (a) position P1 and (b) position P2

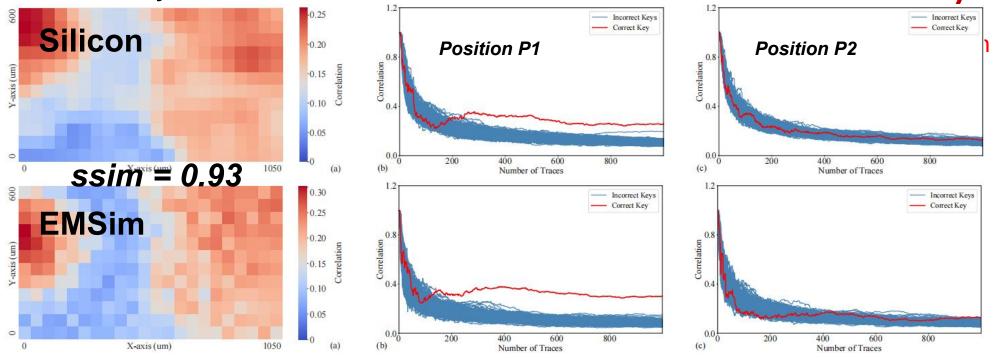

- EMSim vs Silicon Measurements

- Benchmark: 128-bit AES design

- Security Evaluation

- ①180 nm CMOS technology

- 214559 cells and 733662 wires

- ③1.6 mm x 1.3 mm of die size

- (4) supply voltage 1.8 V

- **5** clock frequency 25 MHz

CEMA attacks on the fabricated AES-128: (a) correlation of the correct key as a function of spatial locations. correlation traces as a function of stimuli number for (b) position P1 and (c) Position P2

- EMSim vs Silicon Measurements

- Benchmark: 128-bit AES design

- Simulation Accuracy

- Security Evaluation

- Computation Cost

- 1180 nm CMOS technology

- 214559 cells and 733662 wires

- ③1.6 mm x 1.3 mm of die size

- 4 supply voltage 1.8 V

- ⑤clock frequency 25 MHz

365529 for current analysis

1424 for electromagnetic computation

| Method | Current Simulation | EM Computation |

|--------|--------------------|----------------|

| EMSIM  | 3.860 s            | 3.451 s        |

TABLE II: Real time spent on each simulation time point for AES-128 design.

#### Outline

- Motivation

- Modeling Framework

- Model Analysis

- Simulation Framework

- Case Studies

- EMSim vs ConvEM

- EMSim vs Silicon Measurements

- Conclusions

- we develop the EMSim framework to significantly speed up EM simulation from the layout level, making EM side channel simulation for larger-scale circuits practical.

- We implement multiple techniques, including device model approximation and parasitic network reduction for the current analysis and GPU acceleration for EM computation, to achieve this.

- These simulated EM traces can be used for design-time security evaluation on an IC's resilience against EM side channel attacks.

# Thank You! Any Questions?